# Intel<sup>®</sup> IXF1110 10-Port Gigabit Ethernet Media Access Controller

#### **Datasheet**

The Intel® IXF1110 is a 10-port Ethernet Media Access Controller (MAC) that supports IEEE 802.3 1000 Mbps applications. The device supports a System Packet Interface Level 4 Phase 2 (SPI4-2) system interface to the network processor or ASIC, and implements an internal Serializer/Deserializer (SerDes) to allow direct connection to optical modules. The integration of the SerDes functionality reduces PCB real-estate and system-cost requirements.

### **Applications**

In general, the IXF1110 is appropriate for high-end switching applications where MAC and SerDes functions are not integrated into the system ASIC.

- High-End Optical Ethernet Switches

- Multi-Service Optical Ethernet Switches

- High-End Ethernet LAN/WAN Routers

### **Product Features**

- SerDes interface with optical module connections for Ethernet physical connectivity

- —Integrated termination

- —I<sup>2</sup>C Read/Write capability

- System Packet Interface Level 4 Phase 2 (SPI4-2)

- Capable of data transfers from 10.24 Gbps up to 12.8 Gbps

- -Supports dynamic phase alignment

- —Integrated termination

- Ten independent 1000 Mbps full-duplex Ethernet MAC ports

- 32-bit CPU interface

- Operating Temperature Range:

MIN MAX 0 °C +70 °C

- RMON statistics

- JTAG boundary scan

- Compliant with IEEE 802.3x Standard for flow control

- Jumbo frame support for 9.6 KB packets

- 18 μ CMOS process technology

- Supports IEEE 802.3 fiber autonegotiation, including forced mode

- SFP MSA compatible

- Internal 17.0 KB receive FIFO and 4.5 KB transmit FIFO per port

- Independent enable/disable of any port

- Detection of overly large packets

- Error counters for dropped and errored packets

- CRC calculation and error detection

- Programmable options:

- —Filter packets with errors

- Filter, broadcast, multicast, and unicast address packets

- Automatically pad transmitted packets less than the minimum frame size

- 552-Ceramic Ball Grid Array (CBGA)

- 1.8 V and 2.5 V operation

- Power consumption: 490 mW per-port typical

- Product Ordering Number (MM): HFIXF1110CC.B2: 860817

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> IXF1110 MAC may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel Centrino, Intel Iogo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, VoiceBrick, VTune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2004, Intel Corporation

| 1.0 | Introd | uction    |                                                                     | 13 |

|-----|--------|-----------|---------------------------------------------------------------------|----|

|     | 1.1    |           | You Will Find in This Document                                      |    |

|     | 1.2    | Relate    | d Documents                                                         | 14 |

| 2.0 | Gene   | ral Descr | iption                                                              | 15 |

| 3.0 | Ball A | ssignme   | nts and Ball List Tables                                            | 17 |

|     | 3.1    | Ball Lis  | st Tables                                                           | 18 |

|     |        | 3.1.1     | Balls Listed in Alphanumeric Order by Signal Name                   | 18 |

|     |        | 3.1.2     | Balls Listed in Alphanumeric Order by Ball Location                 | 24 |

| 4.0 | Ball A | .ssignme  | nts and Signal Descriptions                                         | 30 |

|     | 4.1    | Namin     | g Conventions                                                       | 30 |

|     |        | 4.1.1     | Signal Name Conventions                                             |    |

|     |        | 4.1.2     | Register Address Conventions                                        |    |

|     | 4.2    | Interfa   | ce Signal Groups                                                    |    |

| 5.0 | Eunet  | ional Doc | scriptions                                                          | 12 |

| 5.0 |        |           | •                                                                   |    |

|     | 5.1    |           | Access Controller                                                   |    |

|     |        | 5.1.1     | General Description                                                 |    |

|     |        | 5.1.2     | MAC Functions                                                       |    |

|     |        |           | 5.1.2.1 Padding of Undersized Frames on Transmit                    |    |

|     |        |           | 5.1.2.2 Automatic CRC Generation                                    |    |

|     |        | 5.1.3     | Flow Control                                                        |    |

|     |        | 5.1.5     | 5.1.3.1 802.3x Flow Control (Full-Duplex Operation)                 |    |

|     |        | 5.1.4     | Fiber Operation                                                     |    |

|     |        | 5.1.5     | Auto-Negotiation                                                    |    |

|     |        | 5.1.5     | 5.1.5.1 Determining If Link Is Established in Auto-Negotiation Mode |    |

|     |        | 5.1.6     | Forced Mode Operation                                               |    |

|     |        | 5.1.0     | 5.1.6.1 Determining If Link Is Established in Forced Mode           |    |

|     |        | 5.1.7     | Jumbo Packet Support                                                |    |

|     |        | 5.1.8     | RMON Statistics Support                                             |    |

|     |        | 0.1.0     | 5.1.8.1 RMON Statistics                                             |    |

|     |        |           | 5.1.8.2 Conventions                                                 |    |

|     |        |           | 5.1.8.3 Additional Statistics                                       |    |

|     | 5.2    | Syster    | m Packet Interface Level 4 Phase 2                                  |    |

|     |        |           | Data Path                                                           |    |

|     |        |           | 5.2.1.1 Control Words                                               |    |

|     |        |           | 5.2.1.2 EOP Abort                                                   |    |

|     |        |           | 5.2.1.3 DIP4                                                        | 62 |

|     |        | 5.2.2     | Start-Up Parameters                                                 | 63 |

|     |        |           | 5.2.2.1 CALENDAR_LEN                                                | 63 |

|     |        |           | 5.2.2.2 CALENDAR_M                                                  |    |

|     |        |           | 5.2.2.3 DIP2_Thr                                                    |    |

|     |        |           | 5.2.2.4 Loss_Of_Sync                                                |    |

|     |        |           | 5.2.2.5 DATA_MAX_T                                                  |    |

|     |        |           | 5.2.2.6 REP_T                                                       | 64 |

|     |              | 5.2.2.7 DIP4_UnLock                                           | 64 |

|-----|--------------|---------------------------------------------------------------|----|

|     |              | 5.2.2.8 DIP4_Lock                                             |    |

|     |              | 5.2.2.9 MaxBurst1                                             |    |

|     |              | 5.2.2.10MaxBurst2                                             |    |

|     | 5.2.3        | Dynamic Phase Alignment Training Sequence (Data Path De-skew) |    |

|     |              | 5.2.3.1 Training at Start-up                                  | 65 |

|     |              | 5.2.3.2 Periodic Training                                     |    |

|     |              | 5.2.3.3 Training in a Practical Implementation                |    |

|     | 5.2.4        | FIFO Status Channel                                           |    |

|     | 5.2.5        | DC Parameters                                                 |    |

| 5.3 |              | s Interface                                                   |    |

|     | 5.3.1        | Introduction                                                  |    |

|     | 5.3.2        | Features                                                      |    |

|     | 5.3.3        | Functional Description                                        |    |

|     |              | 5.3.3.1 Transmitter Operational Overview                      |    |

|     |              | 5.3.3.2 Transmitter Programmable Driver-Power Levels          |    |

|     |              | 5.3.3.3 Receiver Operational Overview                         |    |

|     | <b>504</b>   | 5.3.3.4 Selective Power-Down                                  |    |

| - 4 | 5.3.4        | Timing and Electrical Characteristics                         |    |

| 5.4 | •            | I Module Interface                                            |    |

|     | 5.4.1        | Introduction                                                  |    |

|     | 5.4.2        | IXF1110 Supported Optical Module Interface Signals.           |    |

|     | 5.4.3        | Functional Descriptions                                       |    |

|     |              | 5.4.3.1 High-Speed Serial Interface                           |    |

|     | <b>5</b> 4 4 | 5.4.3.2 Low-Speed Status Signaling Interface                  |    |

|     | 5.4.4        | I <sup>2</sup> C Module Configuration Interface               |    |

|     |              | 5.4.4.1 General Description                                   | /6 |

|     |              | 5.4.4.2 I <sup>2</sup> C Protocol Specifics                   |    |

|     |              | 5.4.4.4 Clock and Data Transitions                            |    |

|     |              | 5.4.4.5 AC Timing Characteristics                             |    |

| 5.5 | I FD In      | terface                                                       |    |

| 0.0 | 5.5.1        | Introduction                                                  |    |

|     | 5.5.2        | Modes of Operation                                            |    |

|     | 5.5.2        | 5.5.2.1 Mode 0                                                |    |

|     |              | 5.5.2.2 Mode 1                                                |    |

|     | 5.5.3        | LED Interface Signal Description                              |    |

|     | 5.5.4        | Mode 0: Detailed Operation                                    |    |

|     | 5.5.5        | Mode 1: Detailed Operation                                    |    |

|     | 5.5.6        | Power-On, Reset, and Initialization                           |    |

|     | 0.0.0        | 5.5.6.1 Enabling the LED Interface                            |    |

|     | 5.5.7        | LED Data Decodes                                              |    |

|     | 5.5.1        | 5.5.7.1 LED Signaling Behavior                                |    |

| 5.6 | CDITI        | nterface                                                      |    |

| 5.0 | 5.6.1        | General Description                                           |    |

|     | 5.6.2        | Functional Description                                        |    |

|     | 5.0.2        | 5.6.2.1 Read Access                                           |    |

|     |              | 5.6.2.1 Read Access                                           |    |

|     |              | 5.6.2.3 Timing parameters                                     |    |

|     | 5.6.3        | Endian                                                        |    |

| 5.7 |              | (Boundary Scan)                                               |    |

| 0.7 | 01/10        | (Douridary Jouri)                                             |    |

|     |         | 5.7.1 TA      | .P Interface (JTAG)                                      | 91  |

|-----|---------|---------------|----------------------------------------------------------|-----|

|     |         | 5.7.2 TA      | P State Machine                                          | 92  |

|     |         | 5.7.3 Ins     | struction Register and Supported Instructions            | 92  |

|     |         | 5.7.4 ID      | Register                                                 | 92  |

|     |         | 5.7.5 Bo      | undary Scan Register                                     | 93  |

|     |         | 5.7.6 By      | pass Register                                            | 93  |

|     | 5.8     |               |                                                          |     |

|     |         |               | stem Interface Reference Clocks                          |     |

|     |         |               | 3.1.1 CLK125                                             |     |

|     |         |               | 3.1.2 CLK50                                              |     |

|     |         |               | Pl4-2 Receive and Transmit Data Path Clocks              |     |

|     |         |               | AG Clock                                                 |     |

|     |         |               | Clock                                                    |     |

|     |         | 5.8.5 LE      | D Clock                                                  | 94  |

| 5.0 | Applic  | ations        |                                                          | 95  |

|     | • •     |               |                                                          |     |

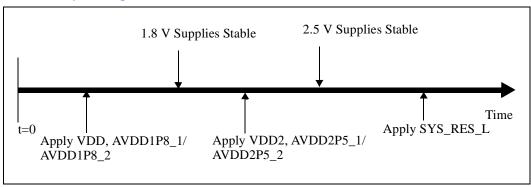

|     | 6.1     |               | pply Sequencing                                          |     |

|     |         |               | wer-Up Sequence                                          |     |

|     | 0.0     |               | wer-Down Sequence                                        |     |

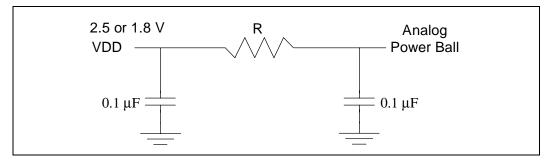

|     | 6.2     |               | wer Filtering                                            |     |

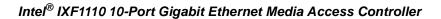

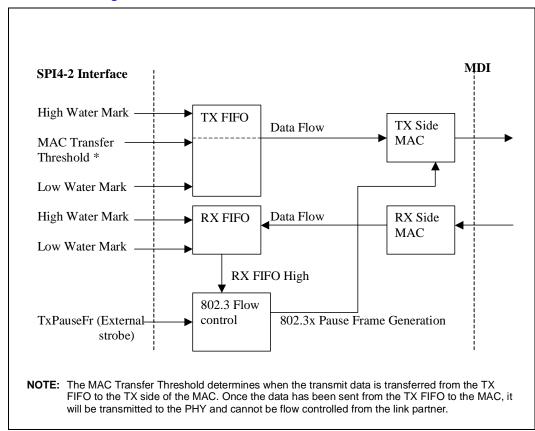

|     | 6.3     |               | nd RX FIFO Operation                                     |     |

|     |         |               | (FIFO                                                    |     |

|     |         |               | 3.1.1 MAC Transfer Threshold                             |     |

|     |         |               | 3.1.3 TX FIFO Drain (IXF1110 Version)                    |     |

|     |         |               | (FIFO                                                    |     |

|     | 6.4     |               | Initialization                                           |     |

|     | 0.4     |               | Pl4-2 Initialization                                     |     |

|     |         |               | 1.1.1 RX SPI4-2                                          |     |

|     |         |               | 1.1.2 TX SPI4-2                                          |     |

|     |         |               | 1.1.3 SerDes                                             |     |

|     |         |               | 1.1.4 CPU                                                |     |

|     | 6.5     | SerDes Po     | wer-Down Capabilities                                    | 101 |

|     |         |               | acing the SerDes Port in Power-Down Mode                 |     |

|     |         | 6.5.2 Bri     | inging the SerDes Port Out of Power-Down Mode            | 102 |

|     | 6.6     | IXF1110 U     | nused Ports                                              | 102 |

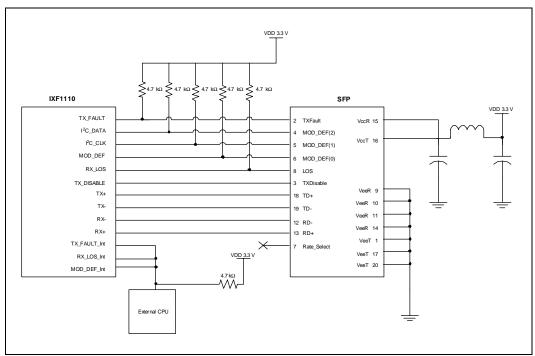

|     | 6.7     | Optical Mo    | dule Connections to the IXF1110                          | 102 |

|     |         | 6.7.1 SF      | P-to-IXF1110 Connection                                  | 102 |

| 7.0 | Electri | aal Spaaifiaa | tions                                                    | 105 |

| .0  |         | •             |                                                          |     |

|     | 7.1     |               | cations                                                  |     |

|     | 7.2     |               | t/Overshoot Specifications                               |     |

|     | 7.3     |               | g Specification                                          |     |

|     | 7.4     |               | ng Specification                                         |     |

|     | 7.5     |               | ause Control Timing Specifications                       |     |

|     | 7.6     | •             | dule Interrupt and I <sup>2</sup> C Timing Specification |     |

|     | 7.7     |               | ming Specifications                                      |     |

|     | 7.8     |               | g Specifications                                         |     |

|     | 7.9     |               | ming Specification                                       |     |

|     | 7.10    | SPI4-2 Tim    | ning Specifications                                      | 120 |

| 8.0            | Regist     | ter Definitions                                                    | 122 |

|----------------|------------|--------------------------------------------------------------------|-----|

|                | 8.1        | Introduction                                                       | 122 |

|                | 8.2        | Document Structure                                                 |     |

|                | 8.3        | Graphical Representation                                           |     |

|                | 8.4        | Per Port Registers                                                 |     |

|                | 8.5        | Memory Map                                                         |     |

|                |            | 8.5.1 MAC Control Registers                                        |     |

|                |            | 8.5.2 MAC RX Statistics Register Overview                          |     |

|                |            | 8.5.3 MAC TX Statistics Register Overview                          |     |

|                |            | 8.5.4 Global Status and Configuration Register Overview            |     |

|                |            | 8.5.5 Global RX Block Register Overview                            |     |

|                |            | 8.5.6 TX Block Register Overview                                   |     |

|                |            | 8.5.7 SPI4-2 Block Register Overview                               | 172 |

|                |            | 8.5.8 SerDes Register Overview                                     | 174 |

|                |            | 8.5.9 Optical Module Interface Block Register Overview             | 176 |

| 9.0            | Packa      | ge Overview                                                        | 178 |

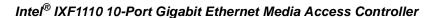

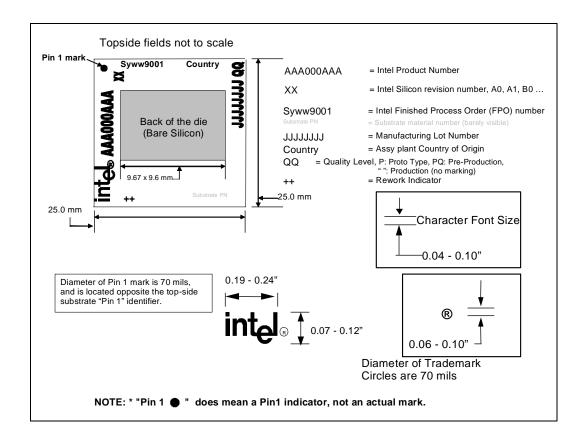

| 0.0            |            | Features                                                           |     |

|                | 9.1<br>9.2 |                                                                    |     |

|                | 9.2        | IXF1110 Package Specifics                                          |     |

|                |            |                                                                    |     |

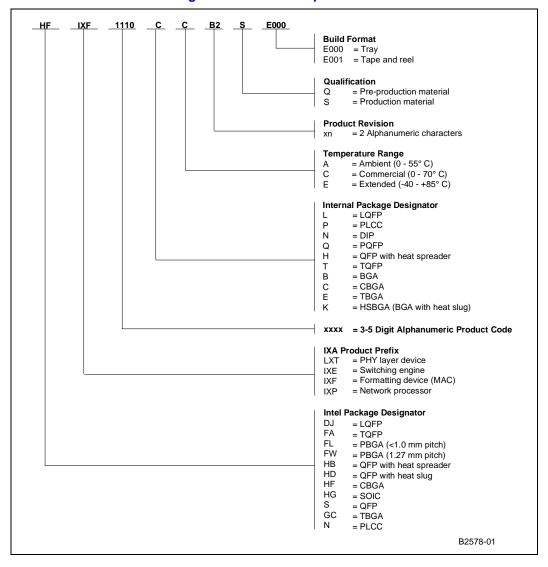

| 10.0           | Produ      | ct Ordering Information                                            | 182 |

| Figures        |            |                                                                    |     |

| <b>Figures</b> |            |                                                                    |     |

|                | 1          | Intel® IXF1110 MAC Block Diagram                                   |     |

|                | 2          | Intel® IXF1110 MAC System Block Diagram                            |     |

|                | 3          | 552-Ball CBGA Assignments (Top View)                               |     |

|                | 4          | Interface Diagram                                                  |     |

|                | 5          | Packet Buffering FIFO                                              |     |

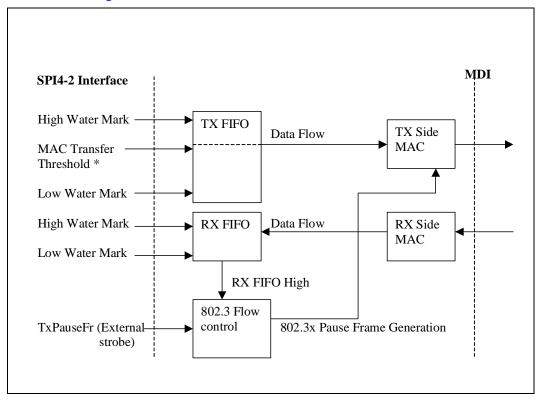

|                | 6          | Ethernet Frame Format                                              |     |

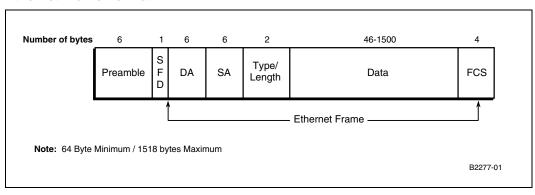

|                | 7          | PAUSE Frame Format                                                 |     |

|                | 8          | Transmit Pause Control Interface                                   |     |

|                | 9          | SPI4-2 Interfacing with the Network Processor or Forwarding Engine |     |

|                | 10         | Data Path State                                                    |     |

|                | 11         | Per-Port State Diagram with Transitions at Control Words           |     |

|                | 12         | DIP-4 Calculation Boundaries                                       |     |

|                | 13         | DIP-4 Calculation Algorithm                                        |     |

|                | 14         | FIFO Status State Diagram                                          |     |

|                | 15         | Example of DIP-2 Encoding                                          |     |

|                | 16         | Data Validity Timing                                               |     |

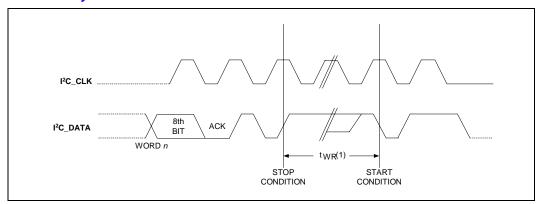

|                | 17         | Start and Stop Definition Timing                                   |     |

|                | 18         | Acknowledge Timing                                                 |     |

|                | 19         | Random Read                                                        |     |

|                | 20         | Byte Write                                                         |     |

|                | 21         | Mode 0 Timing                                                      |     |

|                | 22         | Mode 1 Timing                                                      |     |

|                | 23         | CPU Interface Inputs/Outputs                                       |     |

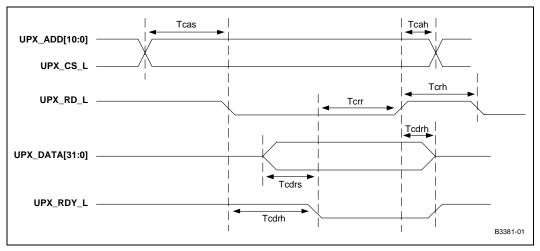

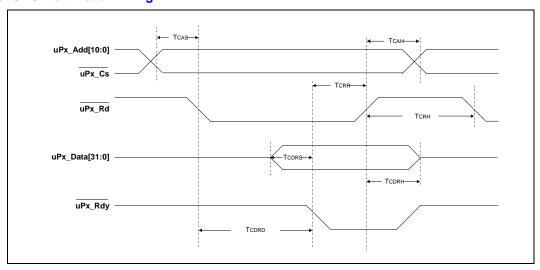

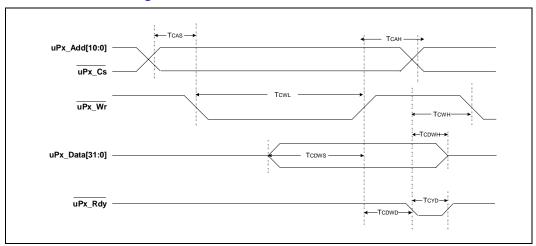

|                | 24         | Read Timing – Asynchronous Interface                               |     |

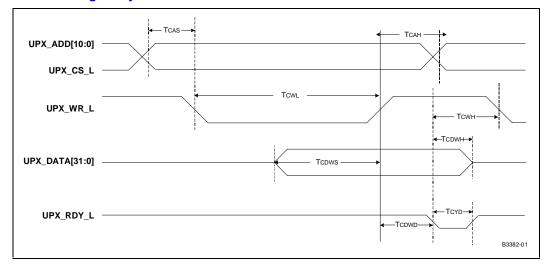

|                | 25         | Write Timing – Asynchronous Interface                              |     |

|                | 26         | Power Sequencing                                                   | 95  |

**Tables**

| 27       | Analog Power Supply Filter Network                            |     |

|----------|---------------------------------------------------------------|-----|

| 28       | Packet Buffering FIFO                                         |     |

| 29       | SFP-to-IXF1110 Connection                                     |     |

| 30       | CPU Port Read Timing                                          |     |

| 31       | CPU Port Write Timing                                         |     |

| 32       | JTAG Timing                                                   |     |

| 33       | Transmit Pause Control Interface                              |     |

| 34       | Optical Module Interrupt Timing                               |     |

| 35<br>36 | I <sup>2</sup> C Write Cycle                                  |     |

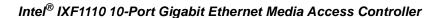

| 30<br>37 | Hardware Reset Timing                                         |     |

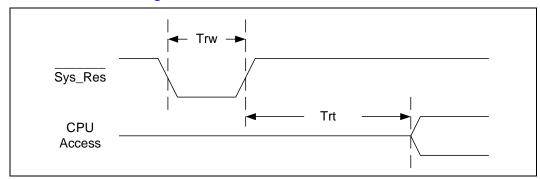

| 38       | LED Timing                                                    |     |

| 39       | SerDes Timing                                                 |     |

| 40       | SPI4-2 Transmit FIFO Status Bus Timing                        |     |

| 41       | SPI4-2 Receive FIFO Status Bus Timing                         |     |

| 42       | Memory Overview                                               |     |

| 43       | Register Overview                                             |     |

| 44       | Intel® IXF1110 MAC 552-Ceramic Ball Grid Array (CBGA) Package |     |

|          | 180                                                           |     |

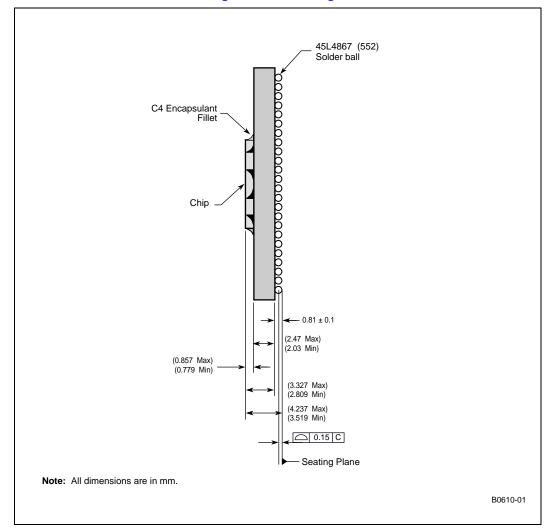

| 45       | Intel®IXF1110 MAC CBGA Package Side View Diagram              |     |

| 46       | Intel® IXF1110 MAC Ordering Information - Sample              | 182 |

|          |                                                               |     |

| 1        | Ball List in Alphanumeric Order by Signal Name                |     |

| 2        | Ball List in Alphanumeric Order by Ball Location              |     |

| 3        | SPI4-2 Interface Signal Descriptions                          |     |

| 4        | SerDes Interface Signal Descriptions                          |     |

| 5        | CPU Interface Signal Descriptions                             |     |

| 6        | Pause Control Interface Signal Descriptions                   |     |

| 7        | Optical Module Interface Signal Descriptions                  |     |

| 8        | LED Interface Signal Descriptions                             |     |

| 9        | JTAG Interface Signal Descriptions                            |     |

| 10       | System Interface Signal Descriptions                          |     |

| 11       | Power Supply Signal Descriptions                              |     |

| 12       | Unused Balls/Reserved                                         |     |

| 13       | Pause Packets Drop Enable Behavior                            |     |

| 14<br>15 | CRC Errored Packets Drop Enable Behavior                      |     |

| 15<br>16 | Valid Decodes for TXPAUSEADD[3:0]                             |     |

| 16       | RMON Additional Statistics Registers                          |     |

| 17<br>10 | SPI4-2 Interface Signal Summary                               |     |

| 18<br>19 | Control Word Format                                           |     |

|          | FIFO Status Format                                            |     |

| 20<br>21 | SerDes Driver TX Power Levels                                 |     |

| 22       | IXF1110-to-SFP Connections                                    |     |

| 23       | LED Signal Descriptions                                       |     |

| 23<br>24 | Mode 0 Clock Cycle to Data Bit Relationship                   |     |

| 24<br>25 | Mode 1 Clock Cycle to Data Bit Relationship                   |     |

| 26       | LED Data Decodes                                              |     |

| 20       | LED Data Decoues                                              | 00  |

| 28 | CPU Interface Signals                                        | 88  |

|----|--------------------------------------------------------------|-----|

| 29 | Recommended JTAG Termination                                 | 91  |

| 30 | Supported Boundary Scan Instructions                         | 92  |

| 31 | Power Sequencing                                             | 96  |

| 32 | Analog Power Balls                                           | 96  |

| 33 | SFP-to-IXF1110 Connection                                    | 103 |

| 34 | Absolute Maximum Ratings                                     | 105 |

| 35 | Operating Conditions                                         | 106 |

| 36 | 2.5 V LVTTL and CMOS I/O Electrical Characteristics          | 107 |

| 37 | LVDS I/O Electrical Characteristics                          | 107 |

| 38 | Undershoot/Overshoot Limits                                  | 108 |

| 39 | CPU Timing Parameters                                        | 109 |

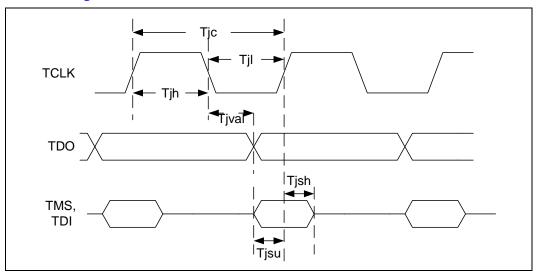

| 40 | JTAG Timing Parameters                                       | 111 |

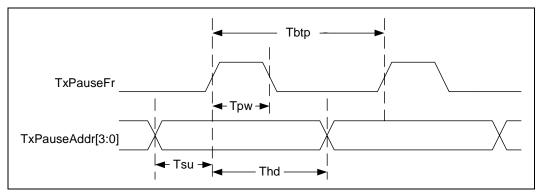

| 41 | Transmit Pause Control Interface Parameters                  | 112 |

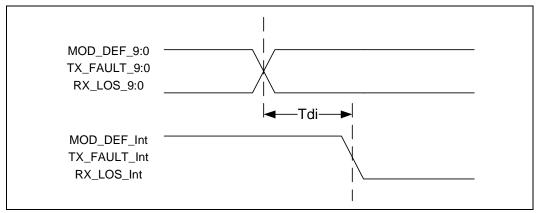

| 42 | Optical Module Interrupt Timing Parameters                   | 113 |

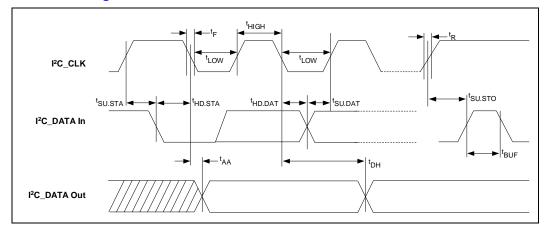

| 43 | I <sup>2</sup> C AC Timing Characteristics                   | 114 |

| 44 | Hardware Reset Timing Parameters                             | 116 |

| 45 | LED Timing Parameters                                        | 117 |

| 46 | Transmitter Characteristics                                  | 118 |

| 47 | Receiver Characteristics                                     | 119 |

| 48 | SPI4-2 Transmit FIFO Status Bus Timing Parameters            | 120 |

| 49 | SPI4-2 Receive FIFO Status Bus Timing Parameters             | 121 |

| 50 | SPI4-2 LVDS Rise/Fall Times                                  | 121 |

| 51 | MAC Control Register Map                                     | 124 |

| 52 | MAC RX Statistics Register Map                               | 125 |

| 53 | MAC TX Statistics Register Map                               | 126 |

| 54 | Global Status and Configuration Register Map                 | 127 |

| 55 | RX Block Register Map                                        | 128 |

| 56 | TX Block Register Map                                        | 129 |

| 57 | SPI4-2 Block Register Map                                    | 130 |

| 58 | SerDes Block Register Map                                    | 130 |

| 59 | Optical Module Interface Block Register Map                  | 131 |

| 60 | Station Address Low (\$ Port_Index + 0x00)                   |     |

| 61 | Station Address High (\$ Port_Index + 0x01)                  |     |

| 62 | FDFC Type (\$ Port_Index + 0x03)                             |     |

| 63 | FC TX Timer Value (\$ Port_Index + 0x07)                     |     |

| 64 | FDFC Address Low (\$ Port_Index + 0x08)                      | 133 |

| 65 | FDFC Address High (\$ Port_Index + 0x09)                     |     |

| 66 | IPG Transmit Time (\$ Port_Index + 0x0C)                     |     |

| 67 | Pause Threshold (\$ Port_Index + 0x0E)                       |     |

| 68 | Max Frame Size (\$ Port_Index + 0x0F)                        |     |

| 69 | FC Enable (\$ Port_Index + 0x12)                             |     |

| 70 | Discard Unknown Control Frame (\$ Port_Index + 0x15)         |     |

| 71 | RX Config Word (\$ Port_Index + 0x16)                        |     |

| 72 | TX Config Word (\$ Port_Index + 0x17)                        |     |

| 73 | Diverse Config (\$ Port_Index + 0x18)                        |     |

| 74 | RX Packet Filter Control (\$ Port_Index + 0x19)              |     |

| 75 | Port Multicast Address Low (\$ Port_Index + 0x1A)            |     |

| 76 | Port Multicast Address High (\$ Port_Index + 0x1B)           |     |

| 77 | MAC RX Statistics (\$ Port Index + 0x20 - Port Index + 0x39) | 140 |

| 78  | MAC TX Statistics (\$ Port_Index + 0x40 - Port_Index + 0x58)     | 144 |

|-----|------------------------------------------------------------------|-----|

| 79  | Port Enable (\$ 0x500)                                           |     |

| 80  | Link LED Enable (\$ 0x502)                                       | 149 |

| 81  | Core Clock Soft Reset (\$ 0x504)                                 |     |

| 82  | MAC Soft Reset (\$ 0x505)                                        | 150 |

| 83  | CPU Interface (\$ 0x508)                                         | 150 |

| 84  | LED Control (\$ 0x509)                                           | 151 |

| 85  | LED Flash Rate (\$ 0x50A)                                        | 151 |

| 86  | LED Fault Disable (\$ 0x50B)                                     | 151 |

| 87  | JTAG ID Revision (\$ 0x50C)                                      |     |

| 88  | RX FIFO High Watermark Ports 0 to 9 (\$ 0x580 - 0x589)           | 153 |

| 89  | RX FIFO Low Watermark Ports 0 to 9 (\$ 0x58A - 0x593)            | 154 |

| 90  | RX FIFO Number of Frames Removed Ports 0 to 9 (\$ 0x594 - 0x59D) | 156 |

| 91  | RX FIFO Port Reset (\$ 0x59E)                                    | 158 |

| 92  | RX FIFO Errored Frame Drop Enable (\$ 0x59F)                     | 159 |

| 93  | RX FIFO Overflow Event (\$ 0x5A0)                                |     |

| 94  | TX FIFO High Watermark Ports 0 to 9 (\$ 0x600 - 0x609)           | 162 |

| 95  | TX FIFO Low Watermark Ports 0 to 9 (\$ 0x60A - 0x613)            | 163 |

| 96  | TX FIFO MAC Transfer Threshold Ports 0 to 9 (\$ 0x614 - 0x61D)   | 165 |

| 97  | TX FIFO Overflow Event (\$ 0x61E)                                | 167 |

| 98  | TX FIFO Drain (\$0x620)                                          |     |

| 99  | TX FIFO Info Out-of-Sequence (\$ 0x621)                          | 169 |

| 100 | TX FIFO Number of Frames Removed Ports 0-9 (\$ 0x622 - 0x62B)    | 170 |

| 101 | SPI4-2 RX Burst Size (\$ 0x700)                                  | 172 |

| 102 | SPI4-2 RX Training (\$ 0x701)                                    | 172 |

| 103 | SPI4-2 RX Calendar (\$ 0x702)                                    | 173 |

| 104 | SPI4-2 TX Synchronization (\$ 0x703)                             | 174 |

| 105 | SerDes Tx Driver Power Level Ports 0-6 (\$ 0x784)                |     |

| 106 | SerDes Tx Driver Power Level Ports 7-9 (\$ 0x785)                | 175 |

| 107 | SerDes TX and RX Power-Down Ports 0-9 (\$ 0x787)                 | 175 |

| 108 | Optical Module Status Ports 0-9 (\$ 0x799)                       |     |

| 109 | Optical Module Control Ports 0-9 (\$ 0x79A)                      |     |

| 110 | I <sup>2</sup> C Control Ports 0-9 (\$ 0x79B)                    |     |

| 111 | I <sup>2</sup> C Data Ports 0-9 (\$ 0x79C)                       |     |

| 112 | Intel® IXF1110 MAC Product Information                           | 182 |

## **Revision History**

| Revision Number: 008<br>Revision Date: August 10, 2004 |                                                                                                                              |  |  |  |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Page #                                                 | Description                                                                                                                  |  |  |  |

| All                                                    | Globally replaced the following: "AVDD" to "AVDD1P8_1, AVDD1P8_2" and "AVDD2" to "AVDD2P5_1, AVDD2P5_2".                     |  |  |  |

| All                                                    | Globally replaced the following: "AIDD" to "AIDD1P8_1, AIDD1P8_2" and "AIDD2" to "AIDD2P5_1, AIDD2P5_2".                     |  |  |  |

| 32                                                     | Corrected ball number for RDAT15_P from K1 to K12 in Table 3 "SPI4-2 Interface Signal Descriptions".                         |  |  |  |

| 124                                                    | Removed Short Runts Threshold Register (\$ Port_Index 0x14) and changed to Reserved in "Table 51 "MAC Control Register Map". |  |  |  |

| Revision Number: 007<br>Revision Date: May 5, 2004 |                                                                                                                      |  |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| Page #                                             | Description                                                                                                          |  |

| 1                                                  | Changed product ordering number to reflect B2 [HFIXF1110CC.B2: 860817].                                              |  |

| 41                                                 | Modified Table 11 "Power Supply Signal Descriptions" [changed AVDD to AVDD1P8_1/2 and AVDD2 to AVDD2P5_1/2].         |  |

| 42                                                 | Added note under Section 5.1.2.1, "Padding of Undersized Frames on Transmit".                                        |  |

| 42                                                 | Modified Section 5.1.2.3.1, "Filter on Unicast Packet Match" [added text to end of paragraph].                       |  |

| 45                                                 | Added Section 5.1.3, "Flow Control".                                                                                 |  |

| 66                                                 | Modified third and fourth paragraphs of Section 5.2.2.2, "CALENDAR_M".                                               |  |

| 97                                                 | Added Section 6.2, "Analog Power Filtering" (IXF1110 only)                                                           |  |

| 116                                                | Modified Section 6.3.1, "TX FIFO" [added note].                                                                      |  |

| 99                                                 | Added Section 6.3.1.3, "TX FIFO Drain (IXF1110 Version)".                                                            |  |

| 110                                                | Added Table 48 "SPI4-2 LVDS Rise/Fall Times".                                                                        |  |

| 126                                                | Modified Table 72 "RX Packet Filter Control (\$ Port_Index + 0x19)" (removed table note from the bit 4 description]. |  |

| 170                                                | Modified Table 114 "SPI4-2 RX Calendar (\$ 0x702)" [changed Register bits 3:0 to Reserved].                          |  |

| 154                                                | Modified Table 88 "JTAG ID Revision (\$ 0x50C)" [added table note 2].                                                |  |

| 163                                                | Added Table 105 "TX FIFO Drain (\$0x620)".                                                                           |  |

| 176                                                | Modified Table 116 "Intel® IXF1010 MAC Product Information" [changed part number and MM number to reflect B2].       |  |

| Revision Number: 006<br>Revision Date: December 30, 2003 |                                                                                   |  |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|

| Page #                                                   | Description                                                                       |  |  |

| NA                                                       | Deleted old Table 19: 1x9-to-IXF1110 Connection                                   |  |  |

| 136                                                      | Modified text under Section 6.5, "SerDes Power-Down Capabilities (IXF1110 Only)". |  |  |

| NA                                                       | Changed Table 98: TX FIFO Port Reset Register (Addr: 0x620) to Reserved.          |  |  |

|        | Revision Number: 005 (Sheet 1 of 2)<br>Revision Date: November 24, 2003                                                                                                                                                                                       |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page # | Description                                                                                                                                                                                                                                                   |

| 1      | Added product ordering and operating temperature range information, and changed SFF-8053, Revision 5.5 Compatible to SFP MSA compatible.                                                                                                                      |

| 17     | Deleted old Figures 6, 7, and 8 (Revision 004) and replaced with Figure 6 "Intel® IXF1110 552-Ball CBGA Assignments (Top View)"                                                                                                                               |

| 18     | Added new Section 3.1, "Intel <sup>®</sup> IXF1110 Ball List Tables" including Table 1 "Intel <sup>®</sup> IXF1110 Ball List in Alphanumeric Order by Signal Name" and Table 2 "Intel <sup>®</sup> IXF1110 Ball List in Alphanumeric Order by Ball Location". |

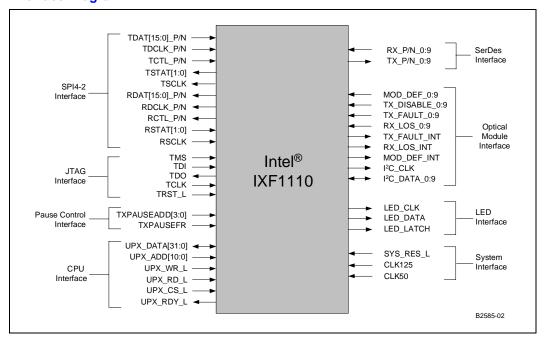

| 30     | Modified Figure 4 "Intel® IXF1110 Interface Diagram".                                                                                                                                                                                                         |

| 31     | Broke up old Table 3 into Table 3 "Intel <sup>®</sup> IXF1110 SPI4-2 Interface Signal Descriptions" through Table 12 "Intel <sup>®</sup> IXF1110 System Interface Signal Descriptions".                                                                       |

| 34     | Modified Table 5 "Intel® IXF1110 CPU Interface Signal Descriptions".                                                                                                                                                                                          |

| 36     | Modified Table 7 "Intel® IXF1110 Optical Module Interface Signal Descriptions".                                                                                                                                                                               |

| 43     | Added note under Section 5.1.2.3.5, "Filter PAUSE Packets".                                                                                                                                                                                                   |

| 43     | Added note under Section 5.1.2.3.6, "Filter CRC Errored Packets".                                                                                                                                                                                             |

| 44     | Added third note to Section 5.1.3, "Fiber Operation".                                                                                                                                                                                                         |

| 46     | Modified text and added note under Section 5.1.4, "Fiber Auto-Negotiation".                                                                                                                                                                                   |

| 46     | Modified Section 5.1.5, "Forced Mode Operation"                                                                                                                                                                                                               |

| 52     | Modified Figure 6 "Intel <sup>®</sup> IXF1110 SPI4-2 Interfacing with the Network Processor or Forwarding Engine".                                                                                                                                            |

| 52     | Added Table 17 "Intel® IXF1110 SPI4-2 Interface Signal Summary".                                                                                                                                                                                              |

| 56     | Added new Section 5.2.1.2, "EOP Abort".                                                                                                                                                                                                                       |

| 65     | Globally modified SFF-8053, Revision 5.5 Compatible to SFP MSA compatible under Section 5.3, "SerDes Interface".                                                                                                                                              |

| 66     | Modified Section 5.3.3, "Functional Description".                                                                                                                                                                                                             |

| 66     | Added Section 5.5.4.1 "Transmitter Programmable Driver-Power Levels".                                                                                                                                                                                         |

| 67     | Added Table 21 "Intel® IXF1110 SerDes Driver TX Power Levels".                                                                                                                                                                                                |

| 68     | Changed Gigabit Interface Converter section to Section 5.6, "Optical Module Interface". Globally changed GBIC to Optical Module.                                                                                                                              |

| 69     | Modified Section 5.4.3.2.1, "MOD_DEF_9:0".                                                                                                                                                                                                                    |

| 69     | Modified Section 5.6.3.2.2, "TX_FAULT_9:0".                                                                                                                                                                                                                   |

| 70     | Modified Section 5.6.3.2.3, "RX_LOS_9:0".                                                                                                                                                                                                                     |

| 86     | Added note to "UPX_RDY" under Section 5.8.2, "Functional Description".                                                                                                                                                                                        |

| 95     | Added note under Section 6.2.1, "TX FIFO".                                                                                                                                                                                                                    |

| 95     | Added note under Section 6.2.1.1, "MAC Transfer Threshold".                                                                                                                                                                                                   |

| 104    | Modified/added Power Consumption Max to Table 49 "Intel® IXF1110 Operating Conditions".                                                                                                                                                                       |

| 105    | Modified Table 36 "Intel® IXF1110 2.5 V LVTTL and CMOS I/O Electrical Characteristics".                                                                                                                                                                       |

| 105    | Added Section 7.2, "Undershoot/Overshoot Specifications".                                                                                                                                                                                                     |

| 107    | Modified Table 39 "Intel® IXF1110 CPU Timing Parameters".                                                                                                                                                                                                     |

| 115    | Modified Table 46 "Intel® IXF1110 Transmitter Characteristics".                                                                                                                                                                                               |

|        | 1                                                                                                                                                                                                                                                             |

|        | Revision Number: 005 (Sheet 2 of 2)<br>Revision Date: November 24, 2003                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| Page # | Description                                                                                                                              |

| 116    | Modified Table 47 "Intel® IXF1110 Receiver Characteristics" (added Common Mode Voltage Spec).                                            |

| 119    | Added caution note under Section 8.0, "Register Definitions".                                                                            |

| 124    | Modified Table 53 "Intel <sup>®</sup> IXFIXF1110 Global Status and Configuration Register Map".                                          |

| 130    | Modified Table 65 "IPG Transmit Time Register (Addr: Port_Index + 0x0C)".                                                                |

| 131    | Modified Table 66 "Pause Threshold Register (Addr: Port_Index + 0x0E)".                                                                  |

| 132    | Modified Table 68 "FC Enable Register (Addr: Port_Index + 0x12)".                                                                        |

| 132    | Modified Table 69 "Short Runts Threshold Register (Addr: Port_Index + 0x14)".                                                            |

| 132    | Modified Table 71 "RX Config Word Register (Addr: Port_Index + 0x16)".                                                                   |

| 133    | Modified Table 72 "TX Config Word Register (Addr: Port_Index + 0x17)".                                                                   |

| 134    | Modified Table 73 "Diverse Config Register (Addr: Port_Index + 0x18)".                                                                   |

| 135    | Modified Table 74 "RX Packet Filter Control Register (Addr: Port_Index + 0x19)" (removed note 2 from bit 4, modified bit 5 description). |

| 137    | Modified Table 77 "MAC RX Statistics Registers (Addr: Port_Index + 0x20 - Port_Index + 0x39)".                                           |

| 146    | Added Table 81 "Core Clock Soft Reset Register (Addr: 0x504)".                                                                           |

| 147    | Added Table 82 "MAC Soft Reset Register (Addr: 0x505)".                                                                                  |

| 155    | Added Table 91 "RX FIFO Port Reset Register (Addr: 0x59E)".                                                                              |

| 165    | Added Section 98, "TX FIFO Port Reset Register (Addr: 0x620)".                                                                           |

| 167    | Modified Table 100 "TX FIFO Number of Frames Removed Ports 0-9 (Addr: 0x622 - 0x62B)".                                                   |

| 170    | Modified Table 103 "SPI4-2 RX Calendar Register (Addr: 0x702)".                                                                          |

| 171    | Modified Table 104 "SPI4-2 TX Synchronization Register (Addr: 0x703) (B0 Silicon Revision)".                                             |

| 173    | Added Table 106 "SerDes Tx Driver Power Level Ports 0-6 Register (Addr: 0x784)".                                                         |

| 173    | Added Table 107 "SerDes Tx Driver Power Level Ports 7-9 Register (Addr: 0x785)".                                                         |

### 1.0 Introduction

This document describes the functionality and operation of the Intel<sup>®</sup> IXF1110 10-Port Gigabit Ethernet Media Access Controller.

#### 1.1 What You Will Find in This Document

This document contains the following sections:

- Section 2.0, "General Description" on page 15

Intel® IXF1110 MAC block diagram system architecture.

- Section 3.0, "Ball Assignments and Ball List Tables" on page 17

Intel® IXF1110 MAC ball grid diagram with two ball list tables (by pin number and signal name)

- Section 4.0, "Ball Assignments and Signal Descriptions" on page 30 Signal naming methodology and signal descriptions.

- Section 5.0, "Functional Descriptions" on page 43

Detailed information about the operation of the Intel<sup>®</sup> IXF1110 MAC including general features, and interface types and descriptions.

- Section 6.0, "Applications" on page 95 Discusses the following:

- "Power Supply Sequencing"

- "TX FIFO and RX FIFO Operation"

- "Reset and Initialization"

- "Optical Module Connections to the IXF1110"

- Section 7.0, "Electrical Specifications" on page 105

Information on the product-operating parameters, electrical specifications, and timing parameters.

- Section 8.0, "Register Definitions" on page 122

Memory map/detailed descriptions and default values for the register set.

- Section 9.0, "Package Overview" on page 178 Intel<sup>®</sup> IXF1110 MAC packaging information.

- Section 10.0, "Product Ordering Information" on page 182

Provides a table with part-number information and diagram to order the Intel® IXF1110 MAC.

### 1.2 Related Documents

| Title                                                                                                                     | Document<br>Number |

|---------------------------------------------------------------------------------------------------------------------------|--------------------|

| Intel® IXF1110 MAC Specification Update                                                                                   | 251436             |

| Intel® IXF1010 and IXF1110 10-Port Gigabit Ethernet Media Access Controllers Design and Layout Guide                      | 250676             |

| Intel® IXF1110 Demo Board Development Kit Manual                                                                          | 250807             |

| Intel® SPI4 Phase 2 Performance in Gigabit Ethernet Media Access Controllers Application Note                             | 250643             |

| Interfacing with the Intel® IXF1010 and Intel® IXF1110 10-Port Gigabit Ethernet Media Access Controllers Application Note | 250856             |

| Intel® IXF1110 Thermal Design Considerations Application Note                                                             | 250289             |

| Flow Control in the Intel® IXF1010 and Intel® IXF1110 10-Port Gigabit Ethernet Media Access Controllers Application Note  | 250236             |

### 2.0 General Description

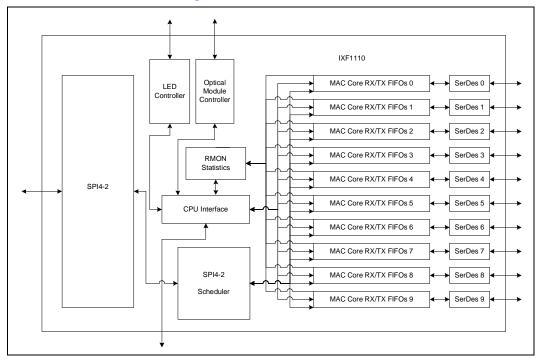

The Intel<sup>®</sup> IXF1110 is a 10-port 1000 Mbps Ethernet Media Access Controller (MAC). The 10 Gigabit interface to the network processor is supported through a System Packet Interface Level 4 Phase 2 (SPI4-2), and the media interface is an integrated Serializer/Deserializer (SerDes).

Figure 1 illustrates the IXF1110 block diagram. Figure 2 represents the IXF1110 system block diagram.

Figure 1. Intel® IXF1110 MAC Block Diagram

Forwarding Engine Network Processor SPI4-2 LED LED Serial IXF1110 CPU Serial-to-Paralle uP IF Interface Converter SerDes/Optical Module Interface Port 9 Optics Module Port 8 Optics Module Port 7 Optics Module Port 5 Optics Module Port 4 Optics Module Port 3 Optics Module Port 2 Optics Module Port 1 Optics Module Port 6 Optics Module Port 0 Optics Module

Figure 2.  $Intel^{\it B}$  IXF1110 MAC System Block Diagram

16 **Datasheet**

### 3.0 Ball Assignments and Ball List Tables

Figure 3 illustrates the IXF1110 552-Ball CBGA assignments. Table 1 and Table 2 provide ball list tables in alphanumeric order by signal name and ball location under Section 3.1, "Ball List Tables" on page 18.

Figure 3. 552-Ball CBGA Assignments (Top View)

|    | AD   | AC   | AB   | AA   | Υ   | W   | V   | U   | Т   | R   | Р   | Ν   | М   | L   | K   | J   | Н   | G   | F   | Е   | D   | С   | В   | Α   | _  |

|----|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

| 1  | AD1  | AC1  | AB1  | AA1  | Y1  | W1  | V1  | U1  | T1  | R1  | L1  | N1  | M1  | L1  | K1  | J1  | H1  | G1  | F1  | E1  | D1  | C1  | B1  | A1  | 1  |

| 2  | AD2  | AC2  | AB2  | AA2  | Y2  | W2  | V2  | U2  | T2  | R2  | P2  | N2  | M2  | L2  | K2  | J2  | H2  | G2  | F2  | E2  | D2  | C2  | B2  | A2  | 2  |

| 3  | AD3  | AC3  | AB3  | AA3  | Y3  | W3  | V3  | U3  | ТЗ  | R3  | P3  | N3  | МЗ  | L3  | КЗ  | J3  | НЗ  | G3  | F3  | E3  | D3  | СЗ  | В3  | А3  | 3  |

| 4  | AD4  | AC4  | AB4  | AA4  | Y4  | W4  | V4  | U4  | T4  | R4  | P4  | N4  | M4  | L4  | K4  | J4  | H4  | G4  | F4  | E4  | D4  | C4  | B4  | A4  | 4  |

| 5  | AD5  | AC5  | AB5  | AA5  | Y5  | W5  | V5  | U5  | T5  | R5  | P5  | N5  | M5  | L5  | K5  | J5  | H5  | G5  | F5  | E5  | D5  | C5  | B5  | A5  | 5  |

| 6  | AD6  | AC6  | AB6  | AA6  | Y6  | W6  | V6  | U6  | T6  | R6  | P6  | N6  | M6  | L6  | K6  | J6  | H6  | G6  | F6  | E6  | D6  | C6  | В6  | A6  | 6  |

| 7  | AD7  | AC7  | AB7  | AA7  | Y7  | W7  | V7  | U7  | T7  | R7  | P7  | N7  | M7  | L7  | K7  | J7  | H7  | G7  | F7  | E7  | D7  | C7  | В7  | A7  | 7  |

| 8  | AD8  | AC8  | AB8  | AA8  | Y8  | W8  | V8  | U8  | Т8  | R8  | P8  | N8  | M8  | L8  | K8  | J8  | H8  | G8  | F8  | E8  | D8  | C8  | В8  | A8  | 8  |

| 9  | AD9  | AC9  | AB9  | AA9  | Y9  | W9  | V9  | U9  | Т9  | R9  | P9  | N9  | М9  | L9  | K9  | J9  | H9  | G9  | F9  | E9  | D9  | C9  | В9  | A9  | 9  |

| 10 | AD10 | AC10 | AB10 | AA10 | Y10 | W10 | V10 | U10 | T10 | R10 | P10 | N10 | M10 | L10 | K10 | J10 | H10 | G10 | F10 | E10 | D10 | C10 | B10 | A10 | 10 |

| 11 | AD11 | AC11 | AB11 | AA11 | Y11 | W11 | V11 | U11 | T11 | R11 | P11 | N11 | M11 | L11 | K11 | J11 | H11 | G11 | F11 | E11 | D11 | C11 | B11 | A11 | 11 |

| 12 | AD12 | AC12 | AB12 | AA12 | Y12 | W12 | V12 | U12 | T12 | R12 | P12 | N12 | M12 | L12 | K12 | J12 | H12 | G12 | F12 | E12 | D12 | C12 | B12 | A12 | 12 |

| 13 | AD13 | AC13 | AB13 | AA13 | Y13 | W13 | V13 | U13 | T13 | R13 | P13 | N13 | M13 | L13 | K13 | J13 | H13 | G13 | F13 | E13 | D13 | C13 | B13 | A13 | 13 |

| 14 | AD14 | AC14 | AB14 | AA14 | Y14 | W14 | V14 | U14 | T14 | R14 | P14 | N14 | M14 | L14 | K14 | J14 | H14 | G14 | F14 | E14 | D14 | C14 | B14 | A14 | 14 |

| 15 | AD15 | AC15 | AB15 | AA15 | Y15 | W15 | V15 | U15 | T15 | R15 | P15 | N15 | M15 | L15 | K15 | J15 | H15 | G15 | F15 | E15 | D15 | C15 | B15 | A15 | 15 |

| 16 | AD16 | AC16 | AB16 | AA16 | Y16 | W16 | V16 | U16 | T16 | R16 | P16 | N16 | M16 | L16 | K16 | J16 | H16 | G16 | F16 | E16 | D16 | C16 | B16 | A16 | 16 |

| 17 | AD17 | AC17 | AB17 | AA17 | Y17 | W17 | V17 | U17 | T17 | R17 | P17 | N17 | M17 | L17 | K17 | J17 | H17 | G17 | F17 | E17 | D17 | C17 | B17 | A17 | 17 |

| 18 | AD18 | AC18 | AB18 | AA18 | Y18 | W18 | V18 | U18 | T18 | R18 | P18 | N18 | M18 | L18 | K18 | J18 | H18 | G18 | F18 | E18 | D18 | C18 | B18 | A18 | 18 |

| 19 | AD19 | AC19 | AB19 | AA19 | Y19 | W19 | V19 | U19 | T19 | R19 | P19 | N19 | M19 | L19 | K19 | J19 | H19 | G19 | F19 | E19 | D19 | C19 | B19 | A19 | 19 |

| 20 | AD20 | AC20 | AB20 | AA20 | Y20 | W20 | V20 | U20 | T20 | R20 | P20 | N20 | M20 | L20 | K20 | J20 | H20 | G20 | F20 | E20 | D20 | C20 | B20 | A20 | 20 |

| 21 | AD21 | AC21 | AB21 | AA21 | Y21 | W21 | V21 | U21 | T21 | R21 | P21 | N21 | M21 | L21 | K21 | J21 | H21 | G21 | F21 | E21 | D21 | C21 | B21 | A21 | 21 |

| 22 | AD22 | AC22 | AB22 | AA22 | Y22 | W22 | V22 | U22 | T22 | R22 | P22 | N22 | M22 | L22 | K22 | J22 | H22 | G22 | F22 | E22 | D22 | C22 | B22 | A22 | 22 |

| 23 | AD23 | AC23 | AB23 | AA23 | Y23 | W23 | V23 | U23 | T23 | R23 | P23 | N23 | M23 | L23 | K23 | J23 | H23 | G23 | F23 | E23 | D23 | C23 | B23 | A23 | 23 |

| 24 | AD24 | AC24 | AB24 | AA24 | Y24 | W24 | V24 | U24 | T24 | R24 | P24 | N24 | M24 | L24 | K24 | J24 | H24 | G24 | F24 | E24 | D24 | C24 | B24 | A24 | 24 |

|    | AD   | AC   | AB   | AA   | Υ   | W   | V   | U   | Т   | R   | Р   | N   | М   | L   | K   | J   | Н   | G   | F   | Е   | D   | С   | В   | Α   | -  |

Datasheet 17

### 3.1 Ball List Tables

Ball list tables are provided in alphanumeric order by signal name (Table 1) and by ball location order (Table 2).

*Note:* Intel recommends that all unconnected balls be tied to their inactive states through external pull-ups or pull-downs.

### 3.1.1 Balls Listed in Alphanumeric Order by Signal Name

Table 1 shows the ball locations and signal names arranged in alphanumeric order by signal name.

**Signal**

Ball

Table 1. Ball List in Alphanumeric Order by Signal Name

| Signal    | Ball |

|-----------|------|

| AVDD1P8_1 | D1   |

| AVDD1P8_1 | E24  |

| AVDD1P8_2 | P7   |

| AVDD1P8_2 | P18  |

| AVDD1P8_2 | V6   |

| AVDD1P8_2 | V11  |

| AVDD1P8_2 | V14  |

| AVDD1P8_2 | V18  |

| AVDD2P5_1 | Y1   |

| AVDD2P5_2 | N3   |

| AVDD2P5_2 | N22  |

| AVDD2P5_2 | P3   |

| AVDD2P5_2 | P22  |

| AVDD2P5_2 | V10  |

| AVDD2P5_2 | V15  |

| CLK125    | AA5  |

| CLK50     | C21  |

| GND       | В6   |

| GND       | B10  |

| GND       | B15  |

| GND       | B19  |

| GND       | C4   |

| GND       | D4   |

| GND       | D5   |

| GND       | D8   |

| GND       | D12  |

| GND       | D13  |

|           |      |

| Signal | Dali |

|--------|------|

| GND    | D21  |

| GND    | D22  |

| GND    | D24  |

| GND    | E1   |

| GND    | F2   |

| GND    | F6   |

| GND    | F10  |

| GND    | F15  |

| GND    | F19  |

| GND    | F23  |

| GND    | G10  |

| GND    | H4   |

| GND    | H8   |

| GND    | H12  |

| GND    | H13  |

| GND    | H17  |

| GND    | H21  |

| GND    | J10  |

| GND    | J15  |

| GND    | J21  |

| GND    | J23  |

| GND    | K2   |

| GND    | K6   |

| GND    | K9   |

| GND    | K11  |

| GND    | K14  |

| GND    | K16  |

| GND    | K19  |

|        |      |

| Signal | Ball |

|--------|------|

| GND    | K20  |

| GND    | K23  |

| GND    | K24  |

| GND    | L3   |

| GND    | L6   |

| GND    | L10  |

| GND    | L12  |

| GND    | L13  |

| GND    | L15  |

| GND    | L24  |

| GND    | МЗ   |

| GND    | M4   |

| GND    | M8   |

| GND    | M11  |

| GND    | M14  |

| GND    | M17  |

| GND    | M18  |

| GND    | M21  |

| GND    | N4   |

| GND    | N8   |

| GND    | N11  |

| GND    | N14  |

| GND    | N17  |

| GND    | N21  |

| GND    | P1   |

| GND    | P10  |

| GND    | P12  |

| GND    | P13  |

### Intel® IXF1110 10-Port Gigabit Ethernet Media Access Controller

| GND         P15           GND         P21           GND         P23           GND         P24           GND         R1           GND         R2           GND         R3           GND         R6           GND         R10           GND         R11           GND         R14           GND         R19           GND         R23           GND         R24           GND         T7           GND         T8           GND         T10           GND         T15           GND         T17           GND         T18           GND         T21           GND         U4           GND         U12           GND         U12           GND         U13           GND         U16           GND         V2           GND         V3           GND         V13           GND         V16           GND         V16           GND         V16 | Signal | Ball |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| GND         P23           GND         P24           GND         R1           GND         R2           GND         R3           GND         R6           GND         R10           GND         R11           GND         R14           GND         R19           GND         R23           GND         R24           GND         T7           GND         T8           GND         T10           GND         T15           GND         T17           GND         T18           GND         T21           GND         U4           GND         U12           GND         U12           GND         U16           GND         U21           GND         V2           GND         V3           GND         V13           GND         V13           GND         V13           GND         V16                                                     | GND    | P15  |

| GND         P24           GND         R1           GND         R2           GND         R6           GND         R9           GND         R10           GND         R11           GND         R14           GND         R19           GND         R23           GND         R24           GND         T7           GND         T8           GND         T10           GND         T15           GND         T17           GND         T18           GND         T21           GND         U4           GND         U7           GND         U12           GND         U13           GND         U16           GND         U21           GND         V2           GND         V3           GND         V13           GND         V13           GND         V13           GND         V16                                                      | GND    | P21  |

| GND         R1           GND         R2           GND         R6           GND         R9           GND         R10           GND         R11           GND         R14           GND         R19           GND         R23           GND         R24           GND         T7           GND         T8           GND         T10           GND         T15           GND         T17           GND         T18           GND         T21           GND         T23           GND         U4           GND         U7           GND         U12           GND         U13           GND         U16           GND         U21           GND         V2           GND         V3           GND         V13           GND         V13           GND         V13           GND         V16                                                      | GND    | P23  |

| GND         R2           GND         R3           GND         R6           GND         R10           GND         R11           GND         R14           GND         R16           GND         R23           GND         R24           GND         T7           GND         T8           GND         T10           GND         T15           GND         T17           GND         T18           GND         T19           GND         T21           GND         U4           GND         U4           GND         U12           GND         U13           GND         U16           GND         U21           GND         V2           GND         V3           GND         V13           GND         V13           GND         V13           GND         V13           GND         V16                                                     | GND    | P24  |

| GND         R3           GND         R6           GND         R9           GND         R10           GND         R11           GND         R14           GND         R19           GND         R23           GND         T7           GND         T8           GND         T9           GND         T10           GND         T15           GND         T18           GND         T19           GND         T21           GND         U4           GND         U4           GND         U12           GND         U12           GND         U13           GND         U16           GND         U21           GND         V3           GND         V13           GND         V13           GND         V13           GND         V13           GND         V16                                                                               | GND    | R1   |

| GND         R6           GND         R9           GND         R10           GND         R11           GND         R14           GND         R16           GND         R23           GND         R24           GND         T7           GND         T8           GND         T10           GND         T15           GND         T17           GND         T18           GND         T19           GND         T21           GND         U4           GND         U4           GND         U12           GND         U12           GND         U13           GND         U16           GND         U21           GND         V3           GND         V13           GND         V13           GND         V13           GND         V16                                                                                                       | GND    | R2   |

| GND         R9           GND         R10           GND         R11           GND         R14           GND         R19           GND         R23           GND         T7           GND         T8           GND         T9           GND         T10           GND         T15           GND         T18           GND         T19           GND         T21           GND         T23           GND         U4           GND         U7           GND         U8           GND         U12           GND         U13           GND         U16           GND         U21           GND         V3           GND         V13           GND         V13           GND         V13           GND         V13           GND         V16                                                                                                        | GND    | R3   |

| GND         R10           GND         R11           GND         R14           GND         R16           GND         R19           GND         R23           GND         T7           GND         T8           GND         T9           GND         T10           GND         T15           GND         T17           GND         T18           GND         T21           GND         T23           GND         U4           GND         U7           GND         U8           GND         U12           GND         U13           GND         U16           GND         U21           GND         V2           GND         V3           GND         V13           GND         V13           GND         V13           GND         V16                                                                                                        | GND    | R6   |

| GND         R11           GND         R14           GND         R16           GND         R19           GND         R23           GND         T7           GND         T8           GND         T9           GND         T10           GND         T15           GND         T17           GND         T18           GND         T21           GND         T23           GND         U4           GND         U7           GND         U8           GND         U12           GND         U13           GND         U16           GND         U21           GND         V2           GND         V3           GND         V13           GND         V13           GND         V13           GND         V16                                                                                                                                  | GND    | R9   |

| GND         R14           GND         R16           GND         R19           GND         R23           GND         T7           GND         T8           GND         T10           GND         T15           GND         T15           GND         T18           GND         T19           GND         T21           GND         T23           GND         U4           GND         U7           GND         U8           GND         U12           GND         U16           GND         U21           GND         V2           GND         V3           GND         V13           GND         V13           GND         V13           GND         V16                                                                                                                                                                                     | GND    | R10  |

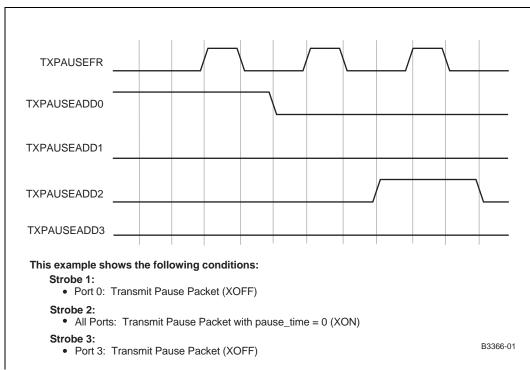

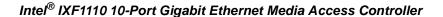

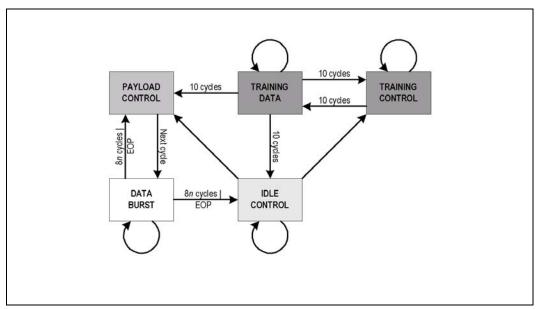

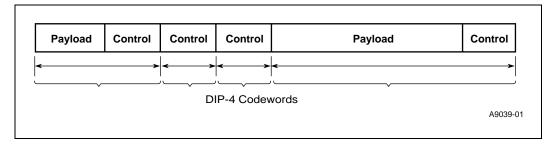

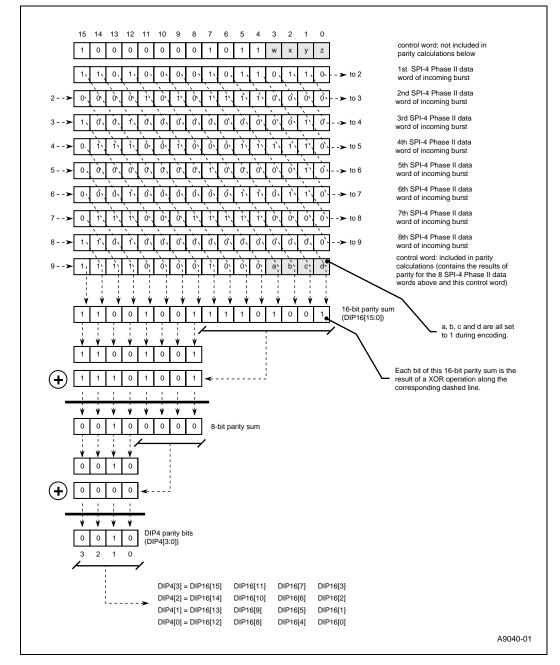

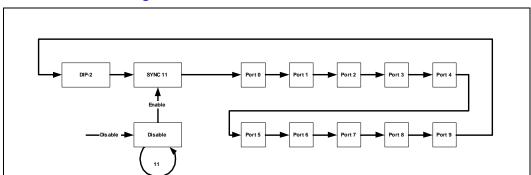

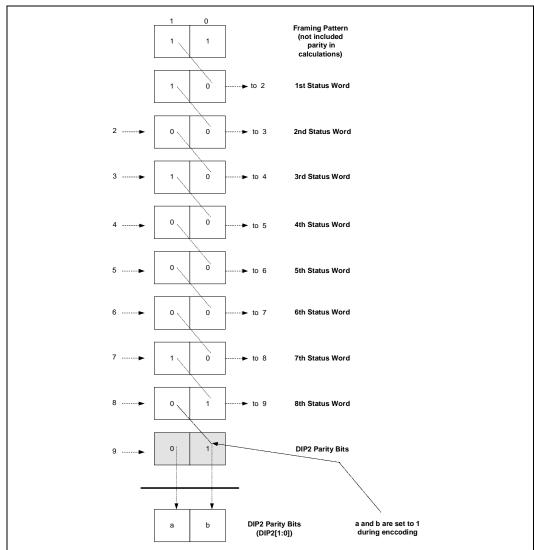

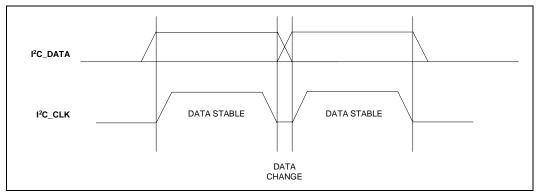

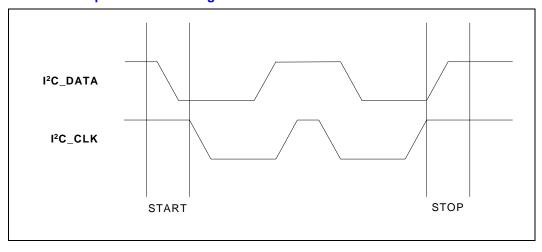

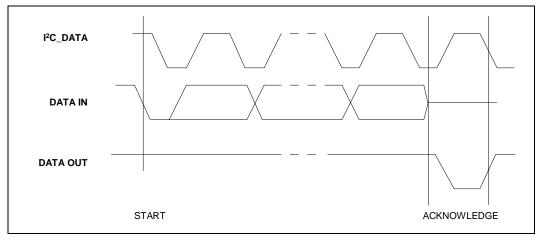

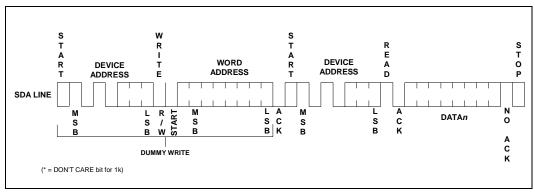

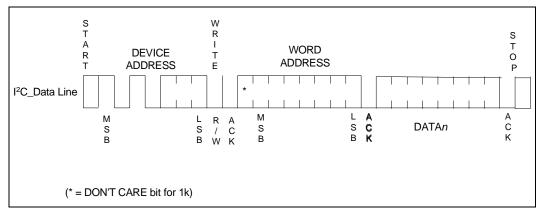

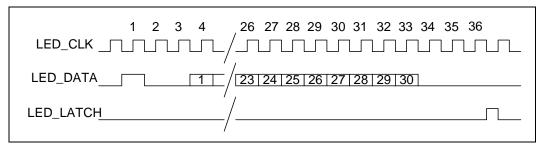

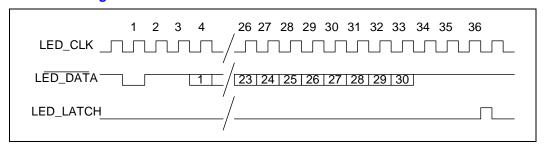

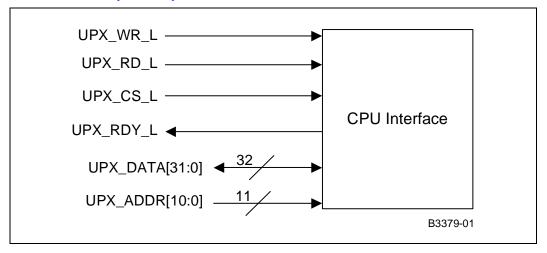

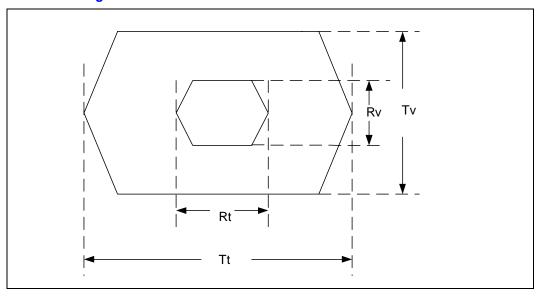

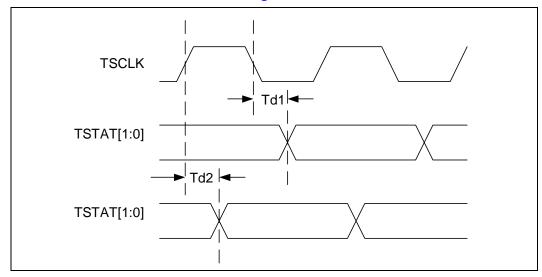

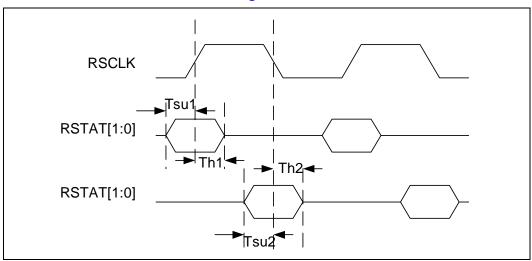

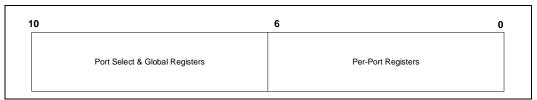

| GND         R16           GND         R19           GND         R23           GND         T7           GND         T8           GND         T9           GND         T10           GND         T15           GND         T17           GND         T18           GND         T21           GND         T23           GND         U4           GND         U7           GND         U8           GND         U12           GND         U13           GND         U16           GND         U21           GND         V3           GND         V13           GND         V13           GND         V13           GND         V13           GND         V16                                                                                                                                                                                     | GND    | R11  |